P0课下提交

本次P0课下提交部分全部为logisim有关内容,五个电路题目我没有一题是一遍过的QAQ,在做每个题目的过程中或多或少都会发现一些疏漏点,本篇笔记的初衷是记录一下做题思路(毕竟.circ文件不支持添加笔记)以及在做题过程中遇到的一些坑点。

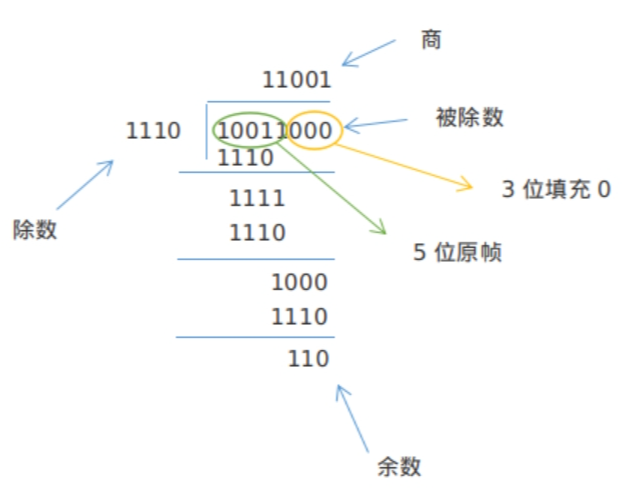

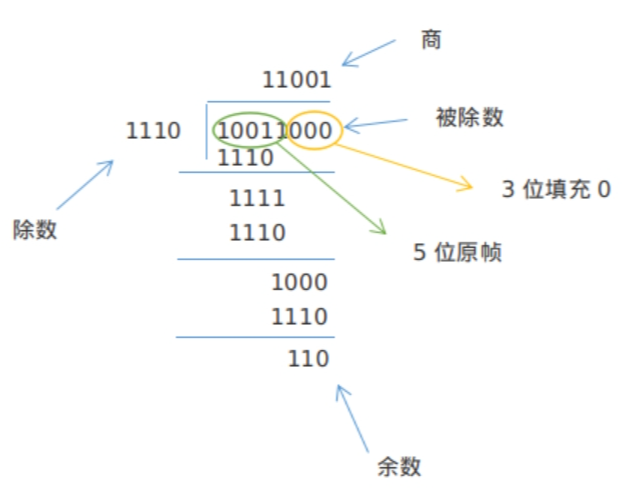

1.CRC校验码的生成

| 名称 | 方向 | 描述 |

|---|---|---|

| A[7 : 0] | I | 8位原数据帧 |

| B[3 : 0] | I | 除数 |

| C[10 : 0] | O | 8位原数据帧+3位余数 |

1.被除数的生成

被除数为8位原数据帧 + (除数位数-1)位0,在题目中具体下来即补全为11位被除数。这时我们发现,按照题目中的提示,按照4位除法来搭建电路,而一个11位数应当可以进行8次4位补位除法(同样参考商的位数是8位可以得到答案,不要被竖式计算过程中似乎计算除法模块小于8次迷惑,做出难以名状的事情)。

2.模二除法

在此题目中涉及到模二除法的使用,这是一个新概念,模二除法在结果上等于两位进行异或的答案,但是进行模二除法的前提是最高位需要为1(已经保证除数的最高位为1),即保证被除数与除数的最高位相同。这样我们可以知道,能进行除法的四位数为```1xxx```,这样得到的余数为```0xxx```,型为```0xxx```的数字不满足进行模二除法的条件,需要进行借位,直到最高位变为1才进行计算,这是根据题目中给出的样例得到的。

在此题目中涉及到模二除法的使用,这是一个新概念,模二除法在结果上等于两位进行异或的答案,但是进行模二除法的前提是最高位需要为1(已经保证除数的最高位为1),即保证被除数与除数的最高位相同。这样我们可以知道,能进行除法的四位数为```1xxx```,这样得到的余数为```0xxx```,型为```0xxx```的数字不满足进行模二除法的条件,需要进行借位,直到最高位变为1才进行计算,这是根据题目中给出的样例得到的。

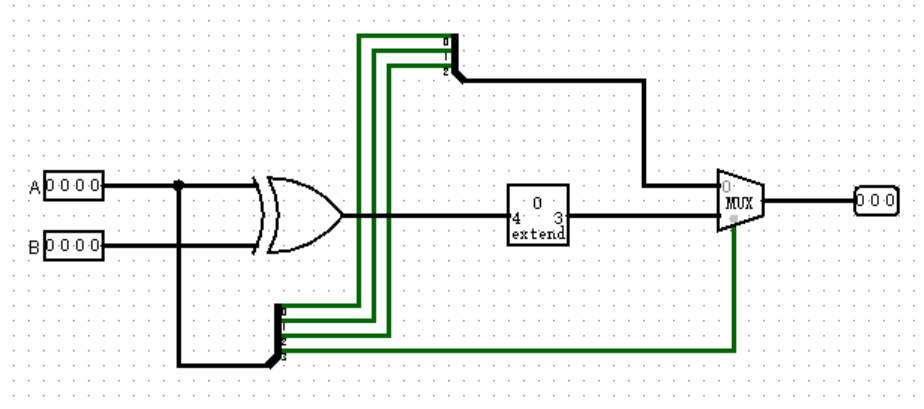

3.电路设计

通过以上分析我们知道,当前补全的四位能否进行模二除法的关键在于它的最高位,如果当前四位数字的最高位为1则进行模二除法,并传递余数到下一级,如果当前最高位为0则将数字左移一位,传递给下一级,如此传递直到最高位为1满足进行除法的条件。由于我们知道余数一定是三位且在进行下一级除法前需要拼接被除数的下一位,因此在四位除法中输出设计为3位。下面给出电路。

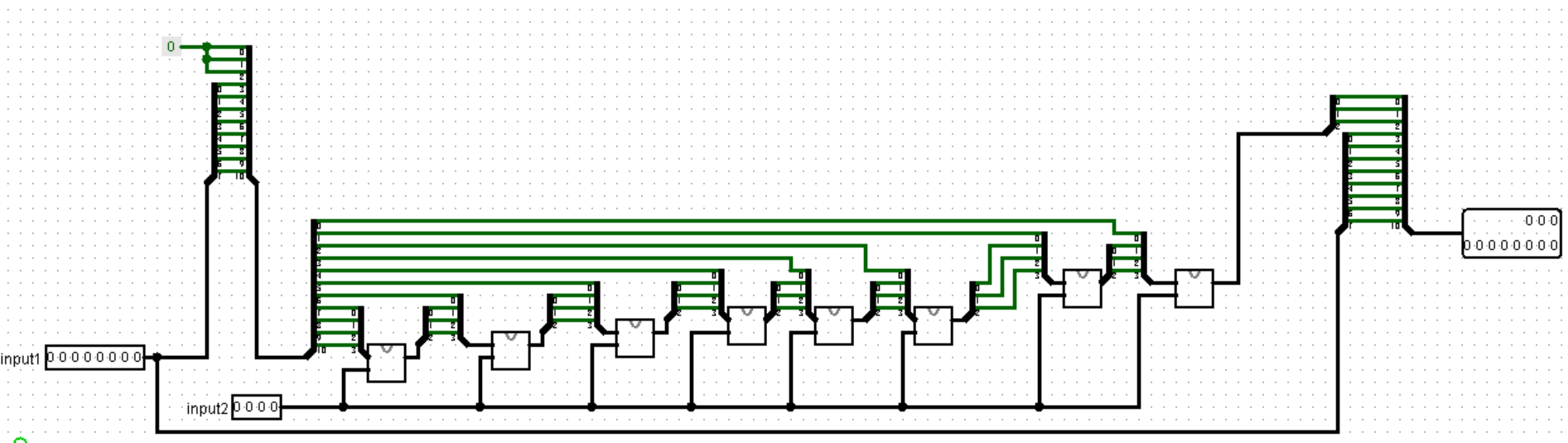

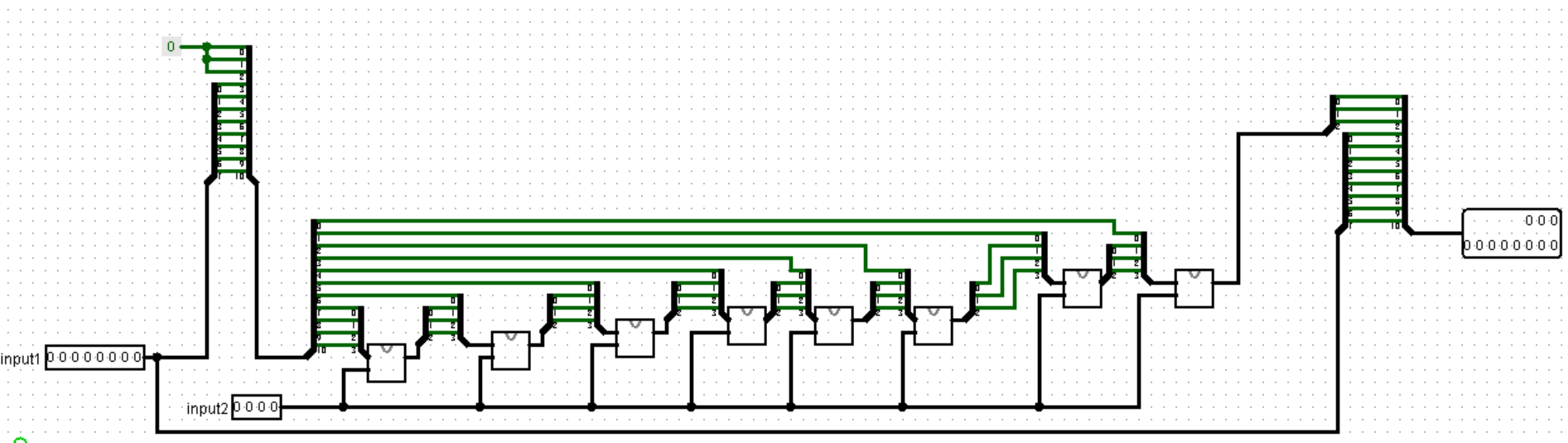

2.主电路搭建

主电路主要实现8级除法的连接(传入下一位),这里需要注意的是在进行输出输出时都需要进行处理,输入时在原数据后补加3位0,输出时在原数据后补加3位余数。此题用到许多的splitter。

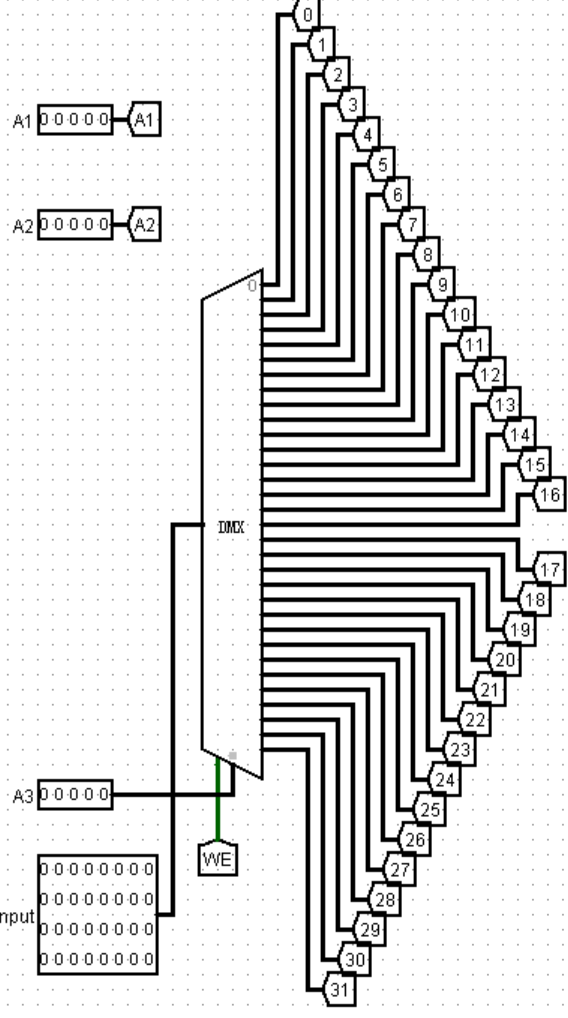

2.实现GRF

这一题主体上的功能比较单一,即对寄存器进行简单的读写操作,但是这个题目中却有很多的细节值得细细品味。而且此题的电路图过于复杂且重复,因此只展示部分电路连接。

1.一个弱智问题MUX与DMX

对于MUX与DMX我要好好品味,毕竟Ppre挂掉就是因为对多路选择器的功能不够熟悉QAQ!。

1.DMX

DMX通常用于输入端选择输入到哪里的情况,短边连接输入信号,长边连接多个可以被选择的输入到的位置。

端口说明:

- 短边连接输入信号(data)

- 长边连接多个输入路径选择

- 腰上一个使能端口(include enable),一个选择输入到第几个路径的输入信号(select),这里需要注意的是一些情况下可以不选择启用使能端口,在启用使能端口时,腰上会出现两个接口点,如何去区分功能?端口上有一个灰色点的是select!

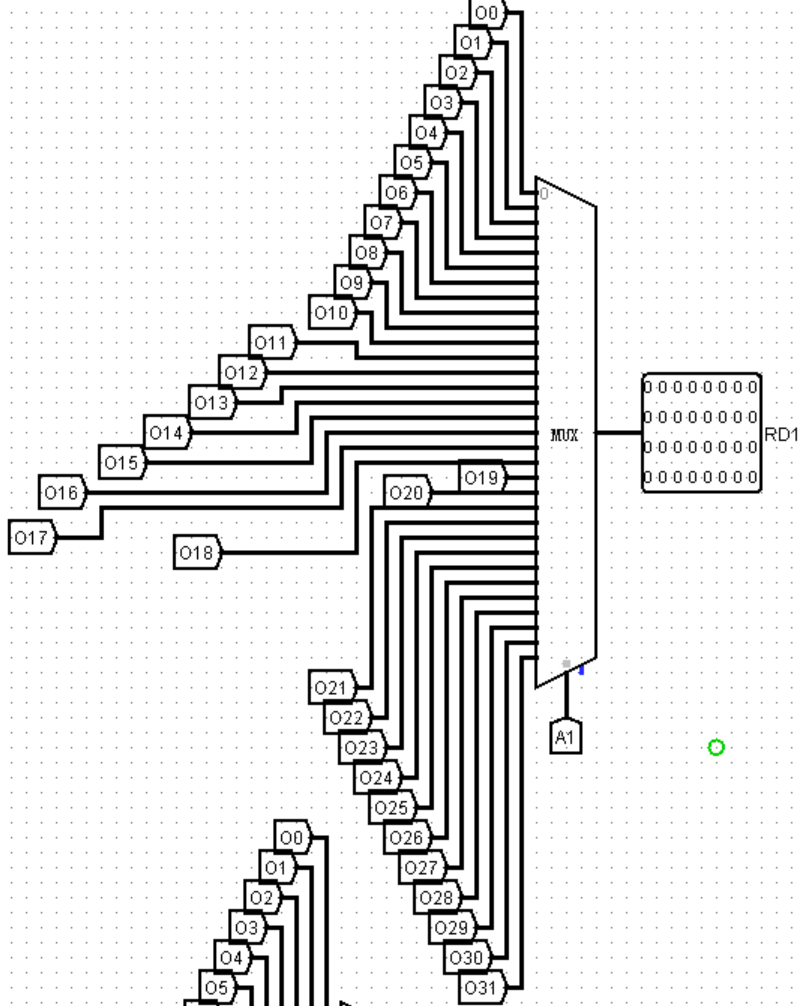

2.MUX

MUX通常用于选择多方数据中的一个来进行输出,长边连接多个可以进行输出的信号,短边进行输出。

端口说明:

短边进行输出(output)

长边上连接多个可供进行输出的信号

腰上一个使能端口(include enable),一个选择输出第几路数据的信号(select),同样,上面标记有灰色点的为选择信号。

3.总结

DMX用于输入到哪里的选择,MUX用于输出哪个的选择。选择信号为腰上标记灰色点的端口。DMX与MUX在此题中配对放置。

使能端的勾选视情况而定。

2.DMX的three-state

在我进行电路搭建的过程中,我习惯性的将three-state设置为no,在此次搭建过程中,由于需要向32个不同的寄存器中写入数据,我发现在写入数据时每当我向新的寄存器写入数据,之前写过的寄存器会被洗掉变回0,这是一个很奇怪的现象,知道我看了讨论区,才知道要将DMX的three-state设置为yes.这背后的原因是什么呢?

在logisim官方文档中,three-state作了如下解释:Specifies whether the unselected outputs should be floating (Yes) or zero (No).即处理没有选择的引脚的输入状态,选择yes即为floating状态,这是一个悬空状态,即不对寄存器输入数据,寄存器中原有的内容不会改变,选择no则会造成zero,即没有被选择的引脚都会输入0,这就会发生原来写入的数据被冲掉的现象。

3.一个坑点

其实DMX的three-state已经可以算作一个坑点,这一点自己动手实验可以发现上一周期存入数据在存入新数据时被洗掉的问题,但可能不知道是three-state出了问题,但是接下来这个坑点可能更不容易被发现,那就是0号寄存器要始终输出0,这一点很容易被忽视,这一点的处理上我选择不使用统一的tunnel处理0号寄存器的使能端,而是将其直接常量化为0,这样可以保证0号寄存器的值始终为寄存器初值0.

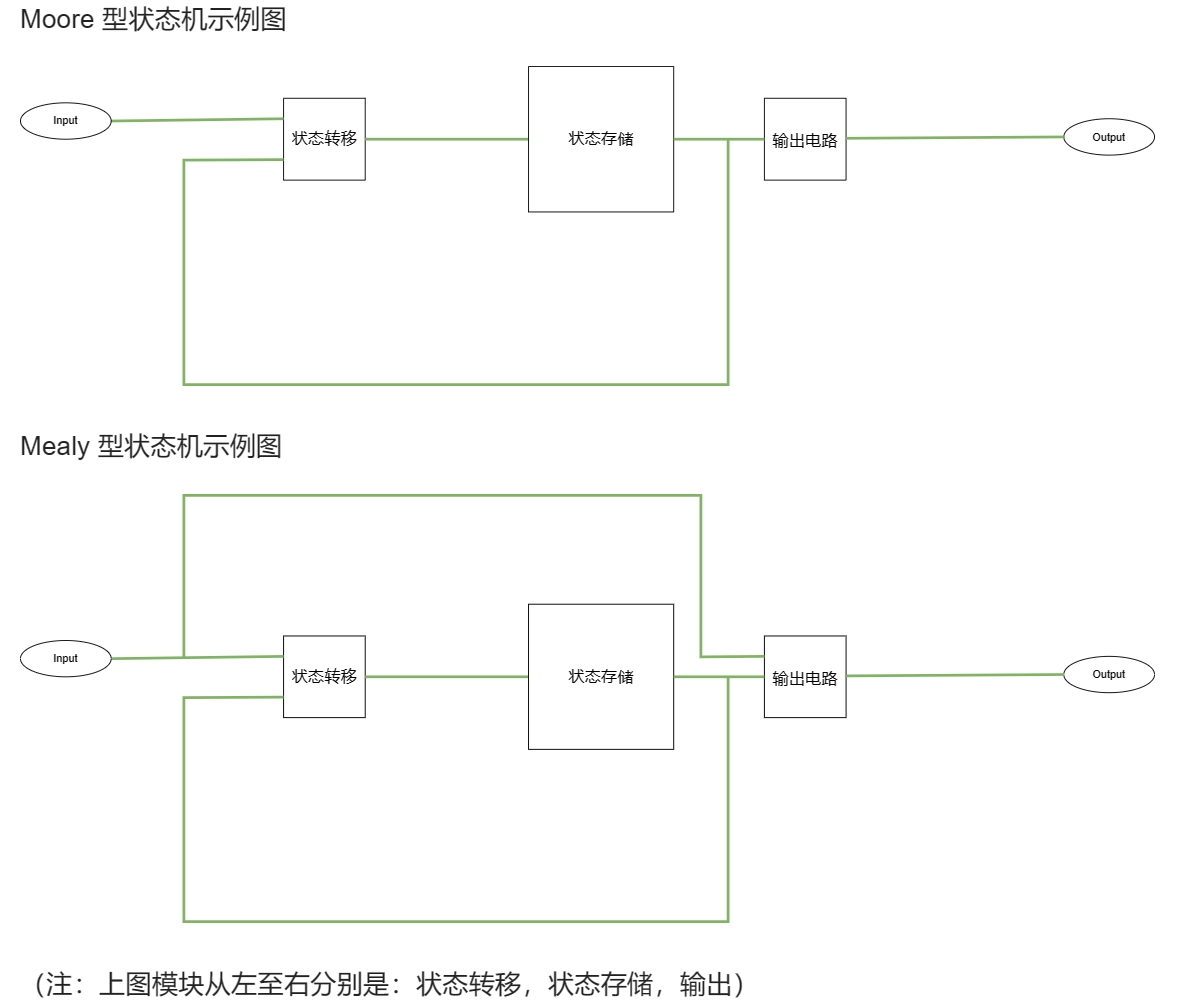

3. Moore与Mealy

对于有限自动机类型的题型,在状态较少的情况下,最常见的情况是利用真值表进行自动绘图,当状态数特别多时,如Pre 上机的俄罗斯方块题目,就不能使用真值表,但是值得庆幸的是,本次作业的两道题目都可以通过真值表完成绘制。

对于两种自动机的辨析,我很喜欢肖利民老师上课时提到的一句话,Moore 型自动机在画真值表时,需要画两张表,下一状态逻辑和输出逻辑分开画,而 Mealy型自动机在画真值表时只需要一张表就可以解决,这是为什么呢?因为Mealy型自动机的两个逻辑模块输入是相同的, Moore型自动机两个逻辑模块的输入不同。但是实际上,当我们选择使用真值表解决问题时,由于分层次绘制的思想,我们总喜欢将下一状态逻辑和输出逻辑封装为不同的子模块,因此在实际绘制时还是相当于两张真值表。因此作业中的两道状态机题目不再给出具体电路,毕竟顶层是模板,底层是真值表。

在绘制有限自动机电路时,熟悉的流水线作业:

- 绘制该种自动机的main模块(模板)

- 绘制status circuit

- 绘制output circuit

从顶层电路中可以看出,Mealy与Moore的主要区别为输出上的区别。当输入后,两种状态机都会next state logic更新次态,但是对于输出,一般采用Mealy型自动机的题目会选择在时钟周期内输入,而不一定在时钟上升沿输入。

简单来说,无论在何种状态机中,一个时钟周期只有一个状态。 但是Moore机我在时钟周期内改变输入,输出不会变,因为输出只与状态有关。Mealy机在周期内改变输入,输出会变,且输出由临时输入与当前状态共同决定。状态只在时钟上升沿(一个周期开始的瞬间)发生改变。

4.logisim导航

这题目一开始我的理解是Mealy型自动机,因为我的理解是hit信号应当是实时更新的,而arrive信号不是。这其实是很扭曲的,你说我设计的是哪一种状态机呢?hit输出信号实时更新,arrive信号等到时钟上升沿到来更新。这不是四不像吗!最关键是我还真设计出来了,hit信号直接从status逻辑中输出,arrive信号从output逻辑中输出。顶层电路实际上不满足任何一种有限自动机。这提醒我不要自己设计新种类自动机QWQ。

实际上,这题虽然没有明说请设计Moore型自动机,却已经给到了充足的暗示,撞到墙壁并将hit信号置高一周期,到达信号需要置位并保持一周期。我们知道,输出信号按照周期更新的是Moore型自动机。

这道题目为了实现hit的按照周期更新,我选择将hit看作一种状态(毕竟是否撞墙确实是一种状态),加入到status的编码中,并作为最高位,这样就是四位状态编码(五个位置对应五个状态)。在output逻辑中对hit进行读取输出。画完状态转移图之后,对应的两个子电路真值表完成信手拈来。

5.正则表达式匹配

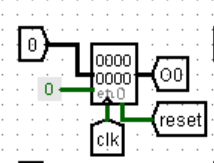

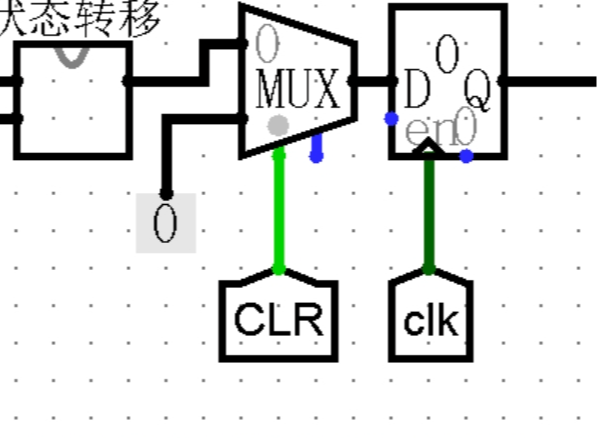

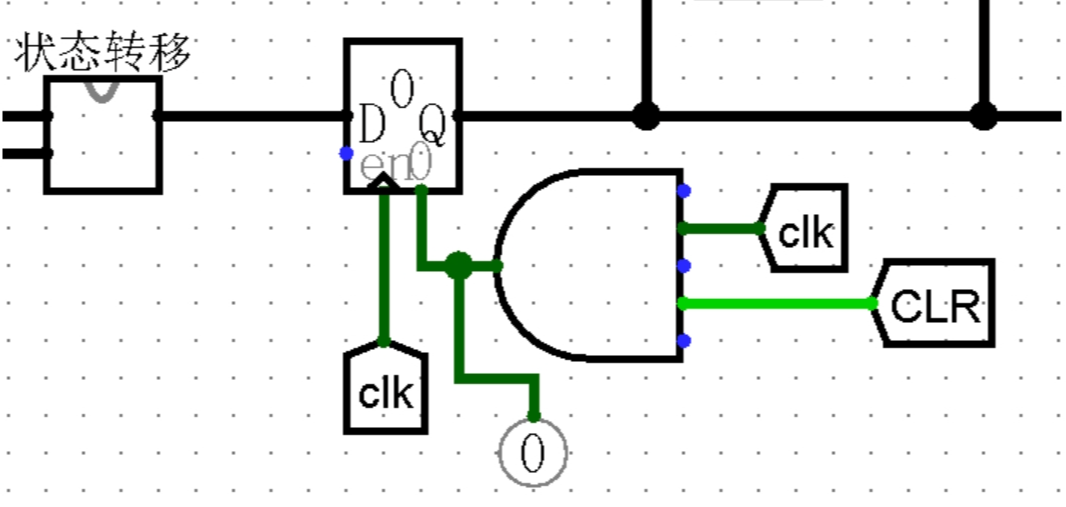

此题涉及到同步复位与异步复位的概念:

- 同步复位:与时钟上升沿同步复位,即时钟上升沿到来时进行复位

- 异步复位:复位信号到来即进行复位,常见的异步复位信号为寄存器的复位信号。

此题目中要求设计Mealy型状态机并实现同步复位,要将复位信号直接接到寄存器上这显然是不对的。我的选择是将复位信号接入到下一状态逻辑中,在复位信号为1时产生的下一状态为00,这样同样可以实现同步复位。但却不太巧妙。

讨论区中介绍了一种通过MUX选择下一状态输入到寄存器的方法,虽然两种办法本质上是相同的,但是明显这种做法更节省电路。

讨论区中还有一种做法如下:这种做法显然是不对的,这种做法中在时钟高电平时均会使复位信号有效。

6.foti

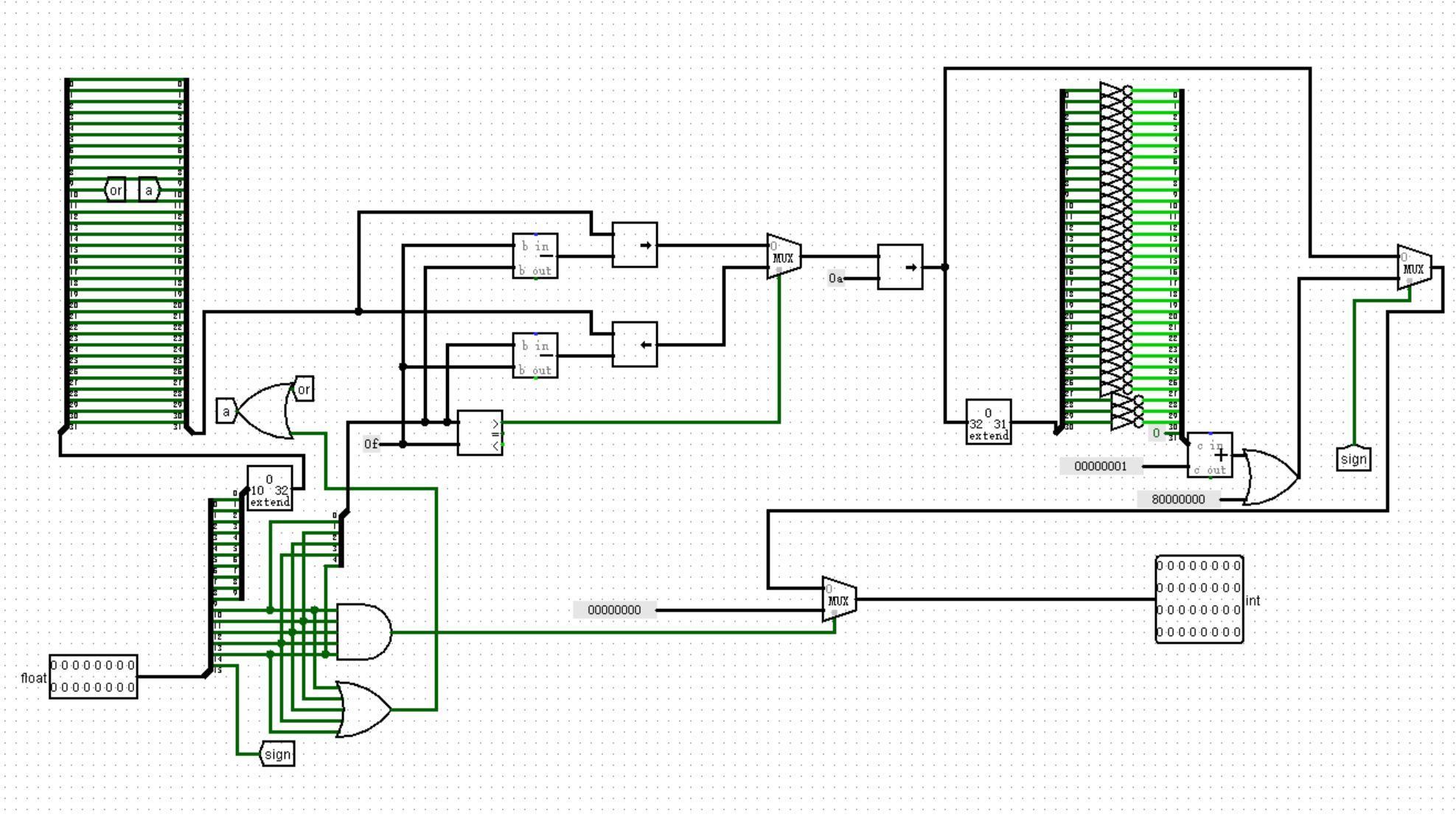

1.主体思路

题目要求输入一个16位的单精度浮点数,输出浮点数的整数部分(有符号),用32位补码表示,超出32位则保留低位。16位单精度浮点数的编码形式为1+5+10.这种固定位数的编码很好处理,有一点像上课讲过的定点浮点数。此题中的定点即为第十位,也就是我们压根不用管移位后的结果,第十位左边的就是整数部分,右边的一律为小数部分。

2.实现细节

1.移位

我们现在知道这就是一个移位+取位的问题。根据给出的公式,我们知道需要判断向左还是向右移位。向左还是向右可以通过comparator实现,比较exponent部分与01111的大小。

2.补码

电路的实现很朴实,我们知道:正数的补码为原码,负数的补码为符号位不变、对应正数的原码取反再加1。在电路里即可按照定义实现:先对符号位进行判断…….

3.对于不同输入状态的判断

这个判断让我很快联想起pre上机中的俄罗斯方块题目,这种判断五位01状态可以使用与门、或门实现,再用MUX选择输出……

3.一个坑点

比较器要选择无符号比较,而不是2的补码比较!

4.电路图

7.结语

两天的搭建过程乐趣无穷,思考电路的架构,细细查找错误…….最现实的是希望下周上机顺利通过!QAQ